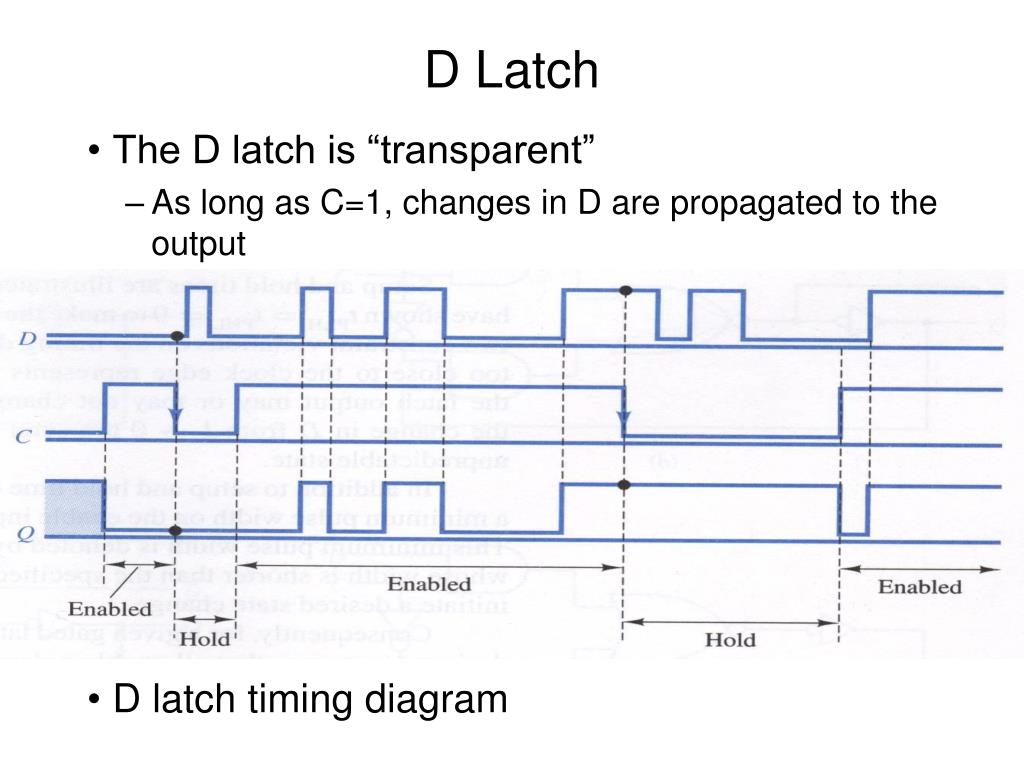

It is clear from the truth table that input data (0 or 1) transmits on output in case of a high CLK input (i.e. Hence, this type of flip-flop is also generally known as a delay flip-flop. As data (0 or 1) provided on input D is received on output Q after a delay equivalent to a clock pulse, therefore output Q shown through the truth table in figure (b) has been represented by Q n+1. Figure (a) just comprises a data input D and clock input CLK, whereas outputs are Q and Q. In figure 5.12, logic symbol and its corresponding truth table has been displayed. Thus, a D flip-flop is a kind of bistable circuit, the input data of which just transfers on output when EN or CLK inputs is high. Therefore, a D type flip-flop is completely absolved of both these types of faults, because an inverter guarantees that S and R will always be in a converse state, therefore formation of a race conduction in D flip-flop is virtually impossible. A D flip-flop has been designed in such a way that it requires just one single data input. Owing to these two significant drawbacks, an RS flip-flop fails to cast a positive impact on several of the applications. Another disadvantage of an RS flip-flop is that a prohibited or forbidden state builds up on it when both of its inputs R and S are inadvertently turn out high (it is also known as race conduction). The creation of two signals in order to drive a flip-flop, is quite damaging in several of the applications (here just keep in mind Q output and forget about Q output for the time being). Thus, two signals S and R are required in order to operate a flip-flop. In order to store a high bit on to it, application of a high S and to store a low bit, a high R is imminent. We know that RS flip-flop comprises two data inputs i.e. D flip-flop is also known as a delay flip-flop, because its input data (0 or 1) transmits on output after some delay equivalent to an interval of a clock pulse.

This D input converges straight on to S input and a complement of D input is received on R input via a NOT gate or inverter. It is quite obvious from the figure that this flip-flop consists of input D (which is called data input) apart from clocked or enabled input. When a single data bit (0 or 1) is desired to be stored, D flip-flop proves very useful for this purpose.įundamentally, D flip-flop is a modified form of an RS clocked flip-flop as can be observed via figure 5.11. When an inverter is fixed alongside an RS flip-flop, an elementary D flip-flop come into existence, as has been revealed via figure 5.10.

In other words, a D flip-flop (also known as data flip-flop or gated D latch or D type latch) consists of a single data input, apart from a clock input. A flip-flop circuit, which need just a single data input, is known as a D flip-flop.

0 Comments

Leave a Reply. |

AuthorWrite something about yourself. No need to be fancy, just an overview. ArchivesCategories |

RSS Feed

RSS Feed